[반도체 공정] 배선공정(Metallization)-1

배선공정(Metallization)

: 금속 배선을 만드는 공정, TSV 형성이 포함됨

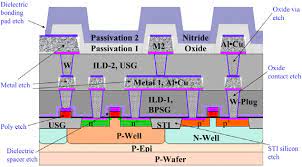

Via, Plug, Interconnection

- 국소 배선: 피치가 좁고 근거리 간 배선 , 저항 높음, Termal budget으로 인해 높은 녹는점 필요

광역 배선: 피치가 넓고 먼 거리 간 배선, 저항 낮음

1. 금속 박막 특성

- 낮은 저항

Resistance(R)= ρ * L/A

= Rs x N *Rs= Sheet Resistance, N=L/W

Sheet Resistance- 회로 설계자가 공정과 관계없이 레이아웃의 N만 정의하면 R을 정의해줄수 있어 편리

Capacitance(C)=ε* L/S

RC delay

- 회로지연시간= R*C

배선 단면적(A) 감소-> 저항 증가

배선간 간격(S) 감소- 기생 C 증가

-> 낮은 비저항, 유전율 가진 소재 필요

Cu & Low K (Si의 유전율(3.9) 이하)

Cu/Low-k는 Al/SiO2 보다 50~70 % 빠르고, Via resistance의 80% 감소를 보인다.

- 열. 화학.기계적 안정성

- 공정 용이성, 낮은 원가

- Adhesion

- 신뢰성

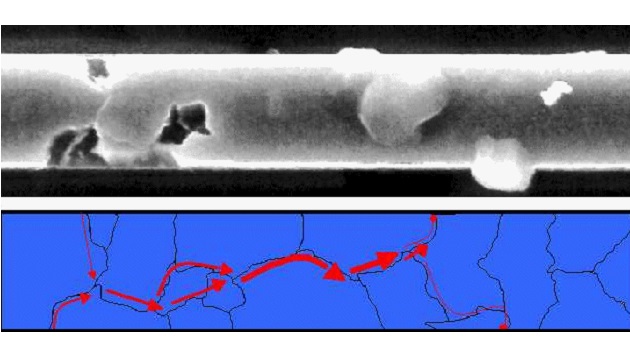

EM(Electromigration): 얇은 박막의 전도체에 높은 전류 밀도로 인하여 금속 이온의 mass transfer가 일어나는 현상

전자가 결정격자의 금속이온과 충돌-> 금속 이온이 격자에서 분리되어 grain boundary를 따라 이동

-> Void- 결정격자에서 금속이온 분리, Open Circuit 발생시킴

Hillock- 이동하던 금속이온이 이동을 방해받아 쌓임, Short 발생시킴

개선- Al alloy(0.5-3% Cu)- grain boundary를 통한 확산 방지

Cu 이용

SM(Stress induced Migration): 실리콘과 금속박막의 열팽창 계수 차이에 의해 발생한 응력이 원인

2. 금속 박막

1) Contact hole

: Gap fill, CMP 중요

텅스텐(W)- 구리보다 약간 높은 저항 가지나, 구리의 오염 위험으로 주로 텅스텐 사용

장: 우수한 Gap fill 특성

단: SI와의 mismatch가 크기 때문에 8000Å이상시 stress 문제 발생-> CD와 depth의 최적화, Barrier 필요

실리콘 내 확산-> Barrier(확산 방지층)필요

Barrier(확산 방지층): TiN- 열적 안정성, 반응성 스퍼터링 이용해 증착

Ti- Glue layer(접착층), TiN에 앞서 증착

ILD(층간 절면막)과 강한 접착력, Si와 Ti silicide를 형성해 contact 저항을 낮춤

, 산소 원자 제거, 산화물 형성 막아줌

7nm 이하는 코발트를 이용하는 추세

2) Interconnection

: Al- 장: 낮은 저항(2.66, 금속 중 4번째로 낮은 저항), 화학적 안정(배리어 필요 x)

Si와 Ohmic contact 형성, 접착성 우수

증착 및 식각 용이

단: 낮은 녹는점(약 660℃)- 후속 공정 문제

EM & SM- 알루미늄은 실리콘 대비 열팽창 계수가 높다

열을 가하는 경우 Compressure -> Hillock

온도 낮추는 경우 Tensil-> Void

Etch시 잔류 Cl가 공기와 반응해 Corrosion을 발생시키기 때문에 In-situ PR Strip이 중요

Junction spiking: 증착 중 Si가 Al 내로 확산되며 Al도 Si으로 상호 확산

Juction Penetration 되면 디바이스 오작동의 원인이 됨(Short Junction & 누설전류)

개선- TiN 배리어 or Al에 1% 정도의 Si를 첨가해 확산 방지

Cu- 장: 낮은 저항(1.67, 금속 중 2번째로 낮은 저항)

높은 녹는점(1,085℃)

높은 신뢰성- 우수한 EM & SM 특성(Al보다 높은 격자/결정입계 확산 활성화 에너지)

단: 산화, Interstitial 확산-> Passivation, Diffusion barrier 필요

식각의 어려움- 휘발성 반응 부산물 만들지 않기 때문-> Damascene 공정 이용

H2 Reactive clean: Al 경우 Pre-sputter cleaning 통해 Al-oxide or Ti-oxide제거

-> Via sidewall에 Redeposition-> Cu 경우 확산으로 인해 문제

-> H2 Reactive clean 이용, 그러나 Humidity adsorption in low-k material 문제 존재

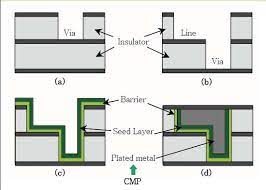

3. Damascene 공정

1) Damascene 공정

: Cu 식각의 어려움으로 인해 Al을 etching 하는 기존 공정과 달리 dielectric을 에칭 하여 Cu를 증착

Via patterning-> Via etch-> Trench patterning-> Trench etch-> PR removal-> Pre-cleaning & Barrier/Seed deposition

-> Cu electroplating-> Cu CMP

Dual Damascene: Via hole과 트렌치가 동시에 형성

피복 능력이 중요하며 Overhang이 최소화되어야 함

2) Material

Cu와 반응하지 않고 (No Solubility), Good Adhesion, Low Resistivity 등이 요구됨

Cu Texture에 영향을 주며 Lattice mismatch, Barrier와 Cu의 deposition method가 중요

- Ta기반의 물질은 Cu와 반응하지 않고 우수한 adhesion 가짐 - Bilayer가 grain boundary mismatch로 가 더 나은 Cu diffusion barrier 특성을 가짐

- TaNx: Amorphous로 low-k 물질과 Cu diffusion을 효과적으로 막음

-Ta: Glue layer로 이용, Cu와 더 나은 adhesion을 가짐

Seed

: Ta 산화방지, Cu의 agglomeration 방지

, 균일한 도금- TaNx는 상대적으로 큰 저향 가져 voltage 인가시 wafer edge와 center 간 무시할 수 없는 voltage drop이 발생 EP thickness of wafer edge >> wafer center

매우 얇은 박막으로 Continuity, Coverage 중요

IPVD-> Device의 소형화에 따라 ALD를 사용하기도 함

3) Electric Plating

- 최근 이용되는 Cu의 damascene process에서는 Via filling에 EP(Electroplating)가 이용됨

- Oxidation at Anode: Cu (solid) -> Cu2+ + 2e-

Reduction at Cathode: Cu2+ + 2e- -> Cu (solid)

- 장: 빠른 증착 속도 super fill(bottom up), good uniformity 등

- Barrier/Seed, electrolyte(pH, additive), plating waveform가 중요

- DC waveforms의 3단계 multi-step으로 이루어짐

- Electrolyte에는 CuSO4, water, H2SO4, HCl, additives가 포함

- Additives: Accelerator(brightener)- 부분적 전류를 증가시킴, disulfide bond가 끊어지면 control이 어려워져 부산물이 생성

Suppressor- Film 형성을 저해, 전형적으로 Nitrogen and Nitrogen/ Sulfur compounds

Leveler- 전류를 감소시켜 평탄성을 향상

Pattern 크기에 따라 증착 속도가 달라 크기가 작은 부분은 overplating

, Terminal Effect로 인해 웨이퍼의 edge가 더 두껍게 plating, E-field가 sharp corners에 집중

-> Leveler로 해결

좁은 패턴 내에 크기가 큰 suppressor는 거의 존재할 수 x, 상대적으로 많은 accelerator가 존재해 bottom up filling이 이루어 짐